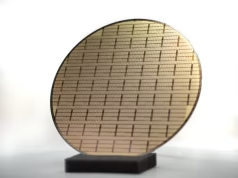

Janus NoC permite a los equipos de diseño lograr un mejor PPA más rápido y con menor riesgo, liberando valiosos recursos de ingeniería para la diferenciación de SoC.

Cadence Design Systems amplia su cartera de sistemas IP con la incorporación de Janus Network-on-Chip (NoC). A medida que proliferan los SoC más grandes y complejos y los sistemas multichip desagregados para adaptarse a las crecientes demandas informáticas actuales, la entrega de datos dentro y entre los componentes de silicio se ha vuelto cada vez más desafiante, lo que afecta la potencia, el rendimiento y el área (PPA).

El Janus NoC gestiona estas comunicaciones simultáneas de alta velocidad de manera eficiente con una latencia mínima, lo que permite a los clientes alcanzar sus objetivos de PPA más rápido y con menor riesgo.

«Cadence es un líder establecido en IP y calidad de diseño, y continuamos invirtiendo en nuestras capacidades fundamentales de interfaz e IP de procesador, IP de sistema, software y servicios de diseño para permitir que nuestros clientes desarrollen diseños diferenciados y desagregados», dijo Boyd Phelps, vicepresidente senior y gerente general del Grupo de Soluciones de Silicio de Cadence. «La incorporación del Cadence Janus NoC a nuestra creciente cartera de sistemas IP es un hito clave en esta estrategia. Nuestra evolución de un proveedor de IP a un socio de diseño de SoC ofrece un mayor valor a nuestros clientes, lo que les permite centrar valiosos recursos de ingeniería en diferenciar su silicio».

Así, Janus NoC aprovecha el legado de herramientas de generación de Tensilica RTL confiables y probadas en el tiempo. Los clientes pueden utilizar la amplia cartera de software y hardware para la simulación y emulación de su NoC y obtener información detallada sobre su rendimiento utilizando la herramienta de análisis de rendimiento del sistema (SPA).

Al permitir la exploración arquitectónica, este flujo da como resultado el mejor diseño de NoC para satisfacer las necesidades del producto. El NoC aprovecha el liderazgo bien establecido de Cadence en IP y calidad, respaldado por la satisfacción del cliente líder en la industria para el soporte técnico.

Por otra parte, Janus NoC mitiga la congestión de enrutamiento y los problemas de tiempo asociados con las complejas interconexiones SoC de hoy en día, que a menudo no se hacen evidentes hasta la implementación física. Abordando las necesidades más apremiantes de la actualidad, el NoC de primera generación proporciona una plataforma para futuras innovaciones, como la compatibilidad con la memoria estándar de la industria y los protocolos de coherencia de E/S.

«Nos complace que Cadence esté expandiendo su cartera de IP invirtiendo en soluciones a nivel de sistema», dijo Suk Lee, vicepresidente y gerente general de la Oficina de Tecnología de Ecosistemas de Intel Foundry. «Dado que un NoC es vital para casi cualquier subsistema de los SoC actuales, apoyamos las iniciativas de Cadence en el desarrollo de su NoC y esperamos que continúen expandiendo su oferta de IP en el futuro».